10. Februar 2017, 20:01

Nachdem ich mir nun eine zweite Kamera dieser Art an geschafft habe, wollte ich nun doch etwas tiefer ein steigen. Eine Analyse bezüglich Sicherheitslücken habe ich nicht vor, mir geht es hauptsächlich darum die Hardware zu analysieren und ggf. die Software zu verbessern oder aus zu tauschen.

Hier erst mal eine Liste mit den gesammelten Daten:

- Typ: Maginon IPC-25 HDC

- Betriebssystem: BusyBox Linux

- Bootloader: U-Boot

- Hersteller der Software: supra Foto-Elektronik-Vertriebs-GmbH

- Link zum GPL Source: http://gpl.supra-elektronik.com/

- CPU: Ralink RT5350F

- Flash: Winbond W25Q64BV (64MBit, 8MByte)

- RAM: 32 Mbyte

- Kamera Modul

- Hersteller: Unbekannt

- Typ: NIF380VX-EMI-V6

- Anschluss: USB

- USB Treiber Baustein: AIT8433 (Alpha Imaging Technology Corp.)

Beim hochladen der Bilder ist mir aufgefallen, das wohl der Pufferkondensator für das PoE zu kein dimensioniert wurde bei der Planung. Aktuell ist ein 100V 100nF auf der Rückseite eingelötet, während der Aufdruck auf der Vorderseite ist.

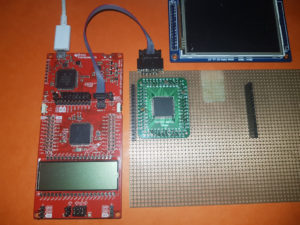

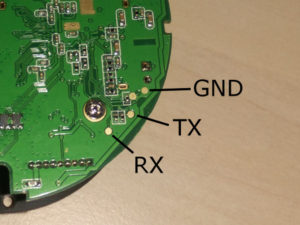

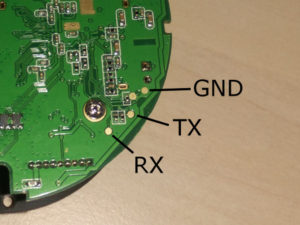

Anschluss der einer Seriellen Console an das Board über einen 3,3V Serial Adapter.

Dump vom Boot Prozess

Dump vom Bootloader

Der Bootloader ist soweit ich das beurteilen kann der Standard U-Boot aus dem Ralink SDK in der Version 1.1.3.

Die Console gibt auch erst mal nichts spektakuläres her.

Analyse Kameramodul

Mein erster versuch die Kamera per USB an einen Rechner an zu schließen und zu sehen was es alles so aus spuckt ist leider gescheitert. Die Kamera bleibt stumm und wird auch nicht im System angezeigt.

Nachdem ich den Boot Prozess unterbrochen habe, ist mir dabei etwas aufgefallen: Auch hier wurde plötzlich kein USB Kamera Modul angezeigt.

Den Boot Prozess kann man besten unterbrechen wenn man den „daemon“ Prozess direkt nach dem Starten killt, denn sonnst wird der Watchdog an geschmissen und wenn man den „daemon“ killt startet auch der Prozessor nach kurzer Zeit neu. Am besten direkt nach dem die BusyBox Version angezeigt wird.

Die Subprozesse kann man in der Datei „/system/init/ipcam.sh“ auskommentieren, so muss man nicht ständig irgendwas killen.

Der Connector zur Kamera hat noch ein paar zusätzliche Pins: LEDCTRL, LCR, RST

Teilweise erschließt sich ja die Funktion. Also habe ich nochmal in das Bootlog geschaut, es taucht die folgende Log Zeile auf:

RT5350/HD/h264/8433/vienc.c, line 413, H264SetIRCutMode : waiting ait 8433 init over

Kurz danach wird dann auch die Kamera per USB initialisiert. Da wird wohl mit den Pins gespielt um den AIT 8433 zu beleben.

Zum testen habe ich einfach mal den RST Pin auf 5V gelegt und siehe da, die Kamera meldet sich. Habe sie dann nochmal an den PC angeschlossen und sie wird sauber als Kamera installiert.

Die Frage ist nun wie bekomme ich den RST Pin auf high.

Nach mehreren Stunden testen habe ich heraus gefunden, dass der Kerneltreiber manipuliert wurde. Beim öffnen des GPIO Devices meldet sich der Kernel immer mit „ralink gpio release by zqh“ und „clr gpio“. Dem Anschein nach werden alle GPIOs beim schließen des Filedescriptors auf null gesetzt. Sehr toll! Super! Was für ein Freak denkt sich so etwas aus? Ich kann mir momentan kein Szenario vorstellen wo ich das benötigen könnte, selbst wenn der Prozess abstützt, warum soll ich denn das Kamera Modul oder die IR LEDs ausschalten? Was für ein quatsch.

Ich könnt stundenlang so weiter machen, aber genug davon.

Nun gut, hier nochmal die Pinbelegung des Kamera Moduls:

- 5V – VCC

- 5V – VCC

- DM – USB Daten Minus

- DP – USB Daten Plus

- GND – Ground

- LEDCTRL – High wenn IR Filter aktiv

- GND – Ground

- LCR – IR LED Control

- RST – Modul Reset

Nun was interessantes, der uvcvideo Treiber meldet unter anderem das Video Format „MJPEG 1280×720 (30.0 fps)“, daher verstehe ich nicht, warum 720p nur über das Depricated Flash in H.264 auf der Kameraseite geht.

Einige Tests mit den GPIOs ergab folgendes Ergebnis:

- GPIO 0 – Taste am Netzwerkkabel

- GPIO 11 – (LCR) IR LED einschalten (geht nur wenn der IR Filter inaktiv ist)

- GPIO 12 – (RST) Kamera Reset Pin

- GPIO 13 – Gelbe LED am Netzwerkkabel

- GPIO 14 – (LEDCTRL) IR Filter

Netzwerk

Während der ganzen Testerei mit den GPIOs musste ich natürlich immer wieder Dateien per TFTP kopieren, das ging natürlich nur mit Netzwerk. Da ich mit mehreren Versuchen das Netzwerk in Gang zu bekommen kläglich gescheitert bin, musste ich immer der „daemon“ Prozess starten um Netzwerken zu können. Das hatte leider immer den Nachteil, dass das GPIO Device immer belegt wurde, also jedes mal neu starten.

Ich habe es dann doch irgendwann geschafft das Netzwerk starten zu können, habe dafür nochmal das Bootlog angeschaut. Da tauchen dann Kommandozeilen auf die den Internen Switch konfigurieren. Tatsächlich ist das im Script /usr/sbin/network.sh alles hinterlegt, also zack das Script ausgeführt und den udhcpc gestartet.

Video

Nachdem ja die Kamera auch 1280×720 per MJPEG kann, habe ich diese Auflösung in das uvc_stream Programm eingepatchd und erfolgreich getestet.

Der Grundstein ist soweit gelegt, ich denke damit kann man eine eigene Firmware für die Kamera bauen. Und wie es weiter geht seht ihr wenn das Licht an geht, nein quatsch. Ich denke das ich nur ein kleines Script schreiben werde, was den uvc_stream Prozess startet, das Netzwerk Konfiguriert und die GPIOs ein schaltet. Ich bin nicht so der Typ für Aufwändige GUIs und Config Kram, aber vielleicht hilft es jemanden oder jemand Forkt das Ralink SDK für die Kamera, dann kann ich mich gerne daran beteiligen.